為了解決電磁干擾EMI問(wèn)題,設(shè)計(jì)工程師還必須遵循一系列的設(shè)計(jì)規(guī)則和方法:

1.在實(shí)際設(shè)計(jì)中建議使用實(shí)體地和電源層,避免電源和地被分割,這種分割可能導(dǎo)致復(fù)雜的電流環(huán)路。電流環(huán)路越大輻射也越大,所以必須避免任何信號(hào),尤其是時(shí)鐘信號(hào)在分割地上布線。

2.將時(shí)鐘驅(qū)動(dòng)器布局在電路板中心位置而不是電路板外圍,將時(shí)鐘驅(qū)動(dòng)器放置在電路板外圍會(huì)增加磁偶極矩(magnetic dipole moment)。

2.為了進(jìn)一步降低頂層時(shí)鐘信號(hào)線的EMI,好是在時(shí)鐘線兩側(cè)并行布上地線。當(dāng)然,好將時(shí)鐘信號(hào)布在地層與電源層之間的內(nèi)部信號(hào)層上。

4.時(shí)鐘信號(hào)使用4mil到8mil的布線寬度,由于窄的信號(hào)線更容易增加高頻信號(hào)衰減,并降低信號(hào)線之間的電容性耦合。

5.由于直角布線會(huì)增加布線電容并增加阻抗的不連續(xù)性,從而導(dǎo)致信號(hào)劣化,所以應(yīng)該盡量避免直角布線和T型布線。

6.盡量滿足阻抗匹配。絕大多數(shù)情況下,阻抗不匹配會(huì)引起反射,而且信號(hào)完整性也主要取決于阻抗匹配。

7.時(shí)鐘信號(hào)布線不能并行走得太長(zhǎng),否則會(huì)產(chǎn)生重》從而導(dǎo)致EMI增大。一個(gè)較好的辦法是確保這些線之間的間距不小于線寬。

8.在設(shè)計(jì)圖形存儲(chǔ)器子系統(tǒng)時(shí),必須確保時(shí)鐘線遠(yuǎn)離任何PC的I/0連接器,距離保持在至少2.5英寸以上。這些連接器包括并行口、串行口、鍵盤(pán)連接器和監(jiān)視器連接器等。在I/0連接器周?chē)O(shè)置地隔離溝的方式可以將共模輻射限制到小。對(duì)于高頻共模輻射的抑制,推薦使用具有合適阻抗特性的鐵氧體器件,由于鐵氧體的阻抗隨頻率而變化,在高頻區(qū)域鐵氧體的特征更接近一個(gè)電阻而不是電感,并且鐵氧體的電四損耗可用于消除輻射:Tracy6_Mal

9.對(duì)外部或內(nèi)部時(shí)鐘源使用Vdd去耦電容可以降低EMI,去耦電容的布局對(duì)于降低時(shí)鐘源器件封裝的發(fā)射來(lái)說(shuō)非常重要,所有電容都應(yīng)該布局在離vdd管腳20mil的范圍以內(nèi)。去耦電容的值是根據(jù)電容的諧振頻率來(lái)定,對(duì)于時(shí)鐘發(fā)生器較高的頻率而言,100pF左右的電容比較合適。

10.縮短高頻信號(hào)布線長(zhǎng)度以及減小電流環(huán)路面積可有效抑制EMI。同時(shí),在時(shí)鐘源上設(shè)置RC濾波器來(lái)控制上升和下降時(shí)間可降低EMI,因?yàn)檩^慢的上升和下降時(shí)間產(chǎn)生較低的發(fā)射頻率。

11.確保時(shí)鐘芯片的電源管腳緊鄰地管腳可以使電源環(huán)路小化。使電源和地管腳引線并行而且互相靠近,這樣可以有效地降低EMI。

12.當(dāng)信號(hào)噪聲源不能消除時(shí),采用濾波器可以有效地實(shí)現(xiàn)噪聲抑制。EMT濾波器以及鐵氧體磁珠是常用的濾波器,鐵氧體磁珠通過(guò)增加電感來(lái)抑制高頻分量。

采用EMI濾波器消除高頻噪聲

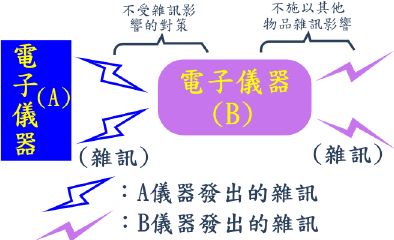

EMI濾波器可以消除電源線上的高頻噪聲,這種濾波器可以在市場(chǎng)買(mǎi)到,EMl濾波器不僅阻止噪聲進(jìn)入系統(tǒng),而且也會(huì)阻止系統(tǒng)產(chǎn)生的噪聲影響系統(tǒng)中的其它部分,具有雙向效果。EMI濾波器的構(gòu)成可以根據(jù)節(jié)點(diǎn)電阻來(lái)確定:高阻抗節(jié)點(diǎn)要求使用電容,而低阻抗節(jié)點(diǎn)要求使用電感。

EML濾波器的結(jié)構(gòu)還可以是旁路電容、L電路、x型電路和T型電路,采用旁路電容的唯一器件就是電容器,當(dāng)連接到濾波器的阻抗很高時(shí)采用旁路電容是一種很好的選擇。

除了時(shí)鐘電路以外,高速器件也會(huì)產(chǎn)生更多的高頻噪聲,這是因?yàn)檩^短的信號(hào)跳變時(shí)間會(huì)使信號(hào)在高頻范圍上有更多的能量。總之,擴(kuò)展頻譜方法提高了系統(tǒng)EMI性能,可以加速產(chǎn)生信號(hào)干擾的產(chǎn)品上市,并且降低封裝和屏蔽方面的成本。與此同時(shí),設(shè)計(jì)工程師應(yīng)該使用所有可能的方法和設(shè)計(jì)規(guī)則來(lái)降低EMI。

本文一共分三篇,其他兩篇閱讀課點(diǎn)擊:

1、采用擴(kuò)展頻譜方法減少EMI同題(上)

2、采用擴(kuò)展頻譜方法減少EMI同題(中)

相關(guān)產(chǎn)品電磁干擾EMI整改問(wèn)題可咨詢環(huán)測(cè)威檢測(cè)工程師解決!

免費(fèi)電話:4008-707-283